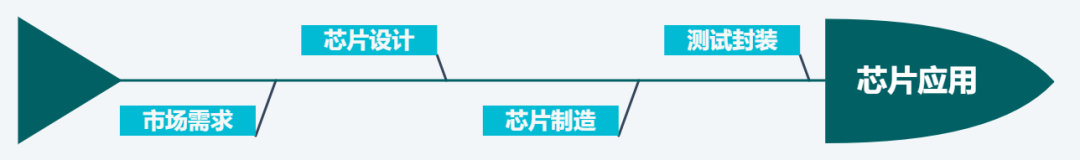

? ? 一(yi)顆芯(xin)片從無到(dao������)有(you),從有(you)需求(qiu)到(dao)最(zui)終(zhong)應用,經歷的(de)(de)(de)是(shi)一(yi)個(ge)(ge)漫長的(de)(de)(de)過程,作(zuo)為人類(lei)科技(ji)巔峰之(zhi)一(yi)的(de)(de)(de)芯(xin)片,凝聚了(le)人們(men)的(de)(de)(de)智慧,而芯(xin)片產(chan)業鏈也是(shi)極其復雜(za)的(de)(de)(de),在此,我大致把(ba)它(ta)歸(gui)為四個(ge)(ge)部分(市場需求--芯片設計--芯片制造--測試封裝),然后再(zai)一一的做(zuo)詳細介紹。

? ?市場需求

? ? 這(zhe)個��������無需(xu)多講,目(mu)前芯片應(ying)用已經滲透到(dao)(dao)我們生活的(de)(de)方方面(mian)面(mian),早晨上(shang)班(ban)騎的(de)(de)共享(xiang)單車,到(dao)(dao)公司刷的(de)(de)IC卡,工作(zuo)時偷偷地打游戲,手(shou)機(ji)卡了還要(yao)換更快的(�������de)(de)手(shou)機(ji),可(ke)以說IC的(de)(de)市場需(xu)求一直都在。

? ?芯片設計

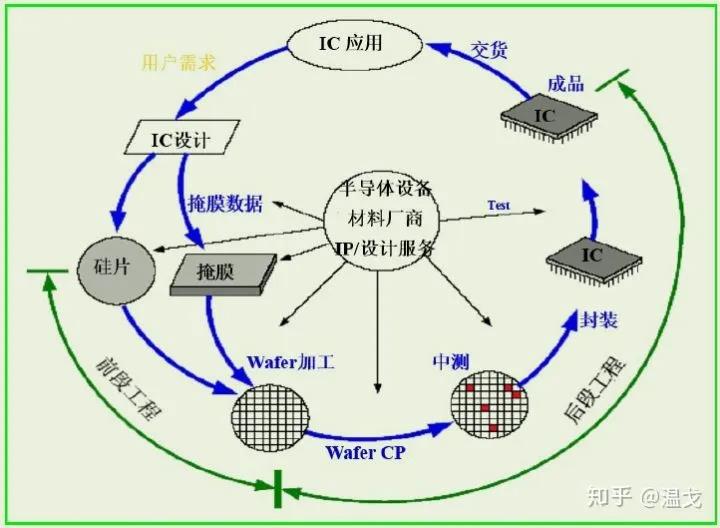

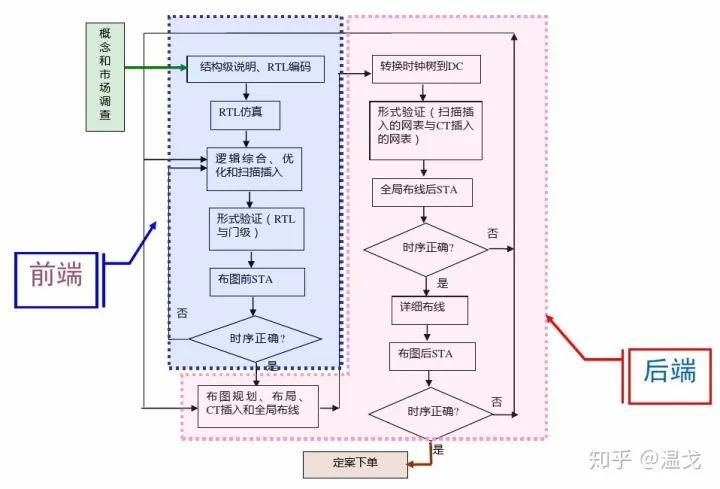

? ? 芯片設計又可以分為兩部分,芯片前端設計和芯片后端設計,整體流程如下圖:

? ?����� 前端設計也(ye)就是從輸入需求到輸出網表的過(guo)程:主要分為以下(xia)六個(ge)步驟:

? ?時序分析(xi)和驗證時出(chu)現(������xian)的(de)錯誤可(ke)能需要反復重(zhong)做前面幾步才能解決,是一(yi)個多(duo)次迭(die)代優化的(de)過程。

? ?下面我(wo)來(lai)仔細介(jie)紹一下這(zhe)六(liu)個步(bu)驟。

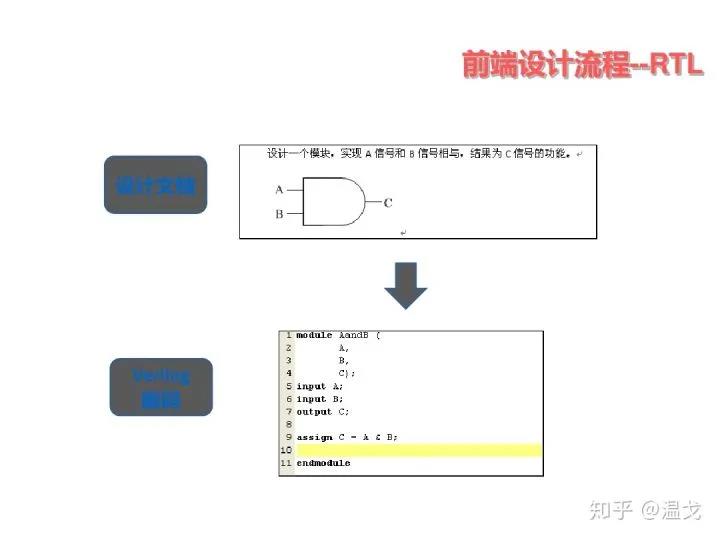

? ? 1、RTL設計(ji)

? ? 在設(she)計(ji)之前我們(men)先要確定芯�������片的工(gong)(gong)藝(yi),比如(ru)是(shi)選(xuan)(xuan)擇TSMC還(huan)是(shi)SMIC,是(shi)7nm,還(huan)是(shi)5nm,而工(gong)(gong)藝(yi)的選(xuan)(xuan)擇也是(shi)受很多因素的制約(如(ru)下圖(tu)),而芯片工(gong)(gong)藝(yi)的選(xuan)(xuan)擇,就是(shi)對(dui)這些因素的權衡。

? ? IC設計的第一步就是制定Spec,這(zhe)個步(bu)驟(zou)(zou)就像(xiang)是在設(she)計(ji)建筑前,要先畫好圖紙一樣,在確(que)定好所有的功能之后在進行(xing)設(she)計(ji),這(zhe)樣才不用再花額外(wai)的時間進行(xing)后續修改。IC 設(she)計(ji)也(ye)需(xu)要經過類�������(lei)似(si)的步(bu)驟(zou)(zou),才能確(que)保設(she)計(ji)出來(lai)的芯片不會有任(ren)何差錯(cuo)。

由(you)文(wen)檔來寫RTL

? ? 而用(y�����ong)RTL實現的(de)各種功能模塊(kuai),來組成一個(ge)實現具體功能的(de)IP,SOC芯片最終(zhong)由(you)SOC integration工(gong)程師把各個(ge)IP集成到一起(qi)。

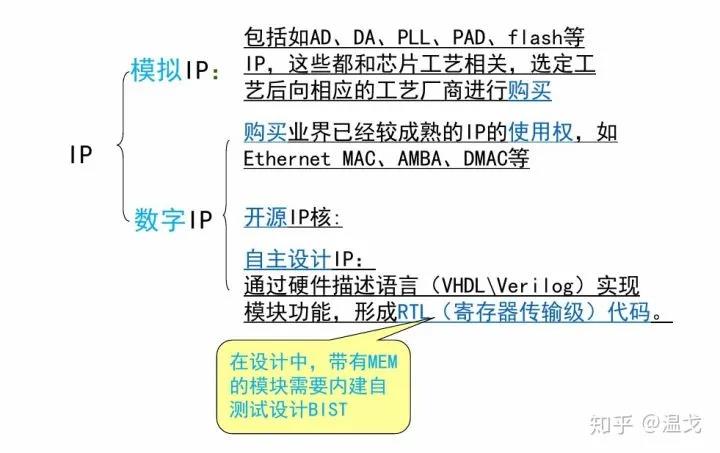

? ? IP又分(fen)為模擬IP和數字(zi)IP,大概可(ke)以做如下的分(fen)類:

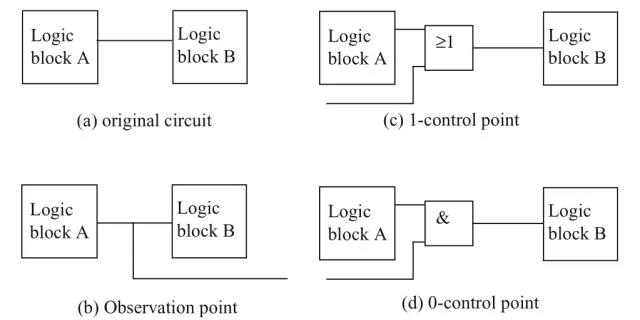

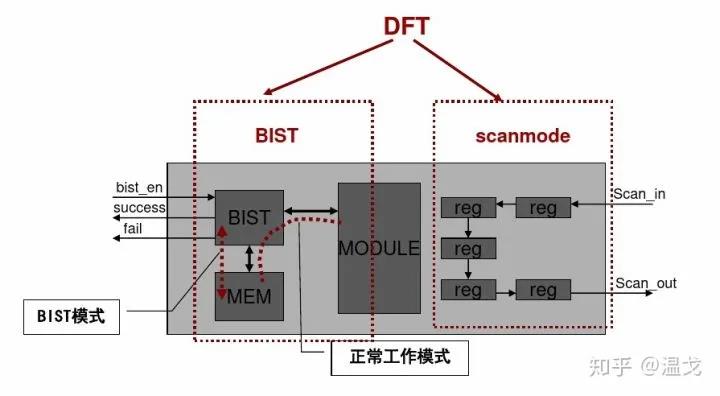

? ? 在(zai)芯(xin)片功能設(she)計完備后,我們還(huan)要做可(ke)�������測(ce)性設(she)計DFT(Design For Test)。

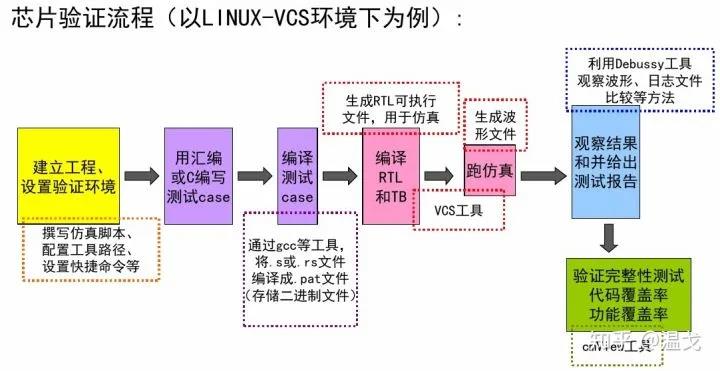

? ? RTL設計(ji)������������最(zui)后要做的(de)就是代(dai)碼的(de)設計(ji)規則檢查。? ? 通過lint, Spyglass等(deng)工具,針(zhen)對(dui)電路進行設計規則檢查,包括����������(kuo)代碼(ma)編寫風格,DFT,命名(ming)規則和(he)電路綜合相關規則等(deng)。? ? 驗證(zheng)是保證(zheng)芯片功能正確性和完整(zheng)性最重要的(de)一環。驗證(zheng)的(de)工作量(liang)也是占整(zheng)����個(ge)芯片開發周期的(de)50%-70%,相應(ying)的(de),驗證(zheng)工程師(shi)與設(she)計工程師(shi)的(de)數量(liang)大概在(zai)2-3:1。? ? 從������驗(yan)證的層次可以分位:模塊級驗(yan)證,子系統級驗(yan)證和系統級驗(yan)證。? ��������? 從驗證的途(tu)�����徑(jing)可以分為:模(mo)擬(simulation),仿(fang)真和(he)形(xing)式驗證(formality check)。

? ? 3、靜(jing)態(tai)時序(xu)分析(STA)? ? 靜(jing)態時(shi)序分(fen)析(xi)(xi)是(shi)套用(yong)特定(ding)的時(shi)序模型(timing model)�����,針對特定(ding)電路,分(fen)析(xi)(xi)其是(shi)否違反designer給定(ding)的時(shi)序限(xian)制(timing constraint)。? ? 目前主流的STA工具(ju)是(shi)synopsys的Prime Time。

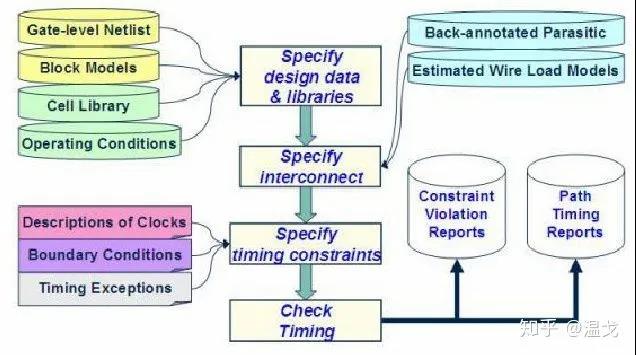

時序(xu)分(fen)析流(liu)程圖

? ? 靜態時(shi)序分析的作用:

? ? 1.確定(ding)芯片最(zui)高工作頻率

? ? 通過時序分析可以控制工(gong)程的綜(zong)合、映(ying)射、布(bu)局布(bu)線等(deng)環節(jie),減(jian)少延�������遲,從而盡可能(neng)提高工(gong)����作(zuo)頻率(lv)。? ? 2. 檢查時(shi)序約(yue)束是否滿足? ? 可以通過時序分(fen)析來(lai)查看目(mu)標模塊是否滿足約束,如�����不滿足,可以定位到(dao)不滿足約束的部分(fen),并給出(chu)具體(ti)原因,進一�������步修改程(cheng)序直(zhi)至滿足要求。? ? 時鐘存在(zai)抖(dou)動、偏移、占空比失(shi)真等不可避(bi)免(mian)的(de)缺陷(xian)。通(tong)過時序分析可以(yi)驗證其對目(mu)標(biao)模������塊的(de)影響。? ? 覆(fu)蓋率作為(wei)一種判斷驗證������充分性(xing)的手段,已成為�������(wei)驗證工作的主導。? ? 從目標(biao)上(shang),可以把覆(fu)蓋率分為兩類:? ? 作(zuo)用(yong):檢(jian)查代碼是(shi)��������������否(fou)冗(rong)余,設(she)計要點是(shi)否(fou)遍歷完全。? ?檢查對象:自(zi)定義的container? ?在設(she)計完成時,要(yao)進(jin)行代碼覆蓋(gai)(gai)率充分性����的sign-off, 對(dui)于(yu)覆蓋(g�����ai)(gai)率未達到100%的情況,要(yao)給出合(he)理的解釋,保(bao)證(zheng)不影(ying)響芯(xin)片的工能。? ? 邏������輯綜合的結果(guo)就是(shi)把設計(ji)實現的RTL代(dai)碼翻譯成門級網表(netlist)的過(guo)程。? ? 在做綜合(he)時要設定約(yue)束條�������件,如電�����(dian)路(lu)面積、時序要求(qiu)等目標參數。? ? 工具:synopsys的���Design compiler, 綜合(he)后把網表交給后端(duan)。? ? 至此我們前(qian)端的工作就結(jie)束啦

? ? 后端�����設計也就(jiu)是從(cong)輸入網表到輸出GDSII文(wen)件的過程:主(zhu)要分為以下六個(ge)步驟:

? ? 在(zai)前端(duan)最(zu�����i)后(hou)一步已(yi)經講過了,在(zai)此不做(zuo)贅(zhui)述。- 不驗證(zheng)電(dian)路本身的正確(que)性(xing)

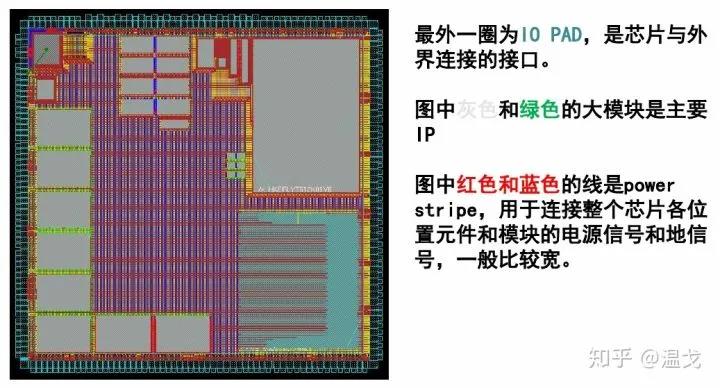

�����? ? 形������(xing)式(shi)驗(yan)證(zheng)的(de)意義在于保障(zhang)芯(xin)片設計(ji)的(de)一致性,一般在邏輯綜(zong)合,布局布線完成后必(bi)須做(zuo)。? ? 工(gong)具:synopsys Formality? ? 物理實現可以分(fen)為三個(ge)部分(fen):? �������? 布(bu)圖規(gui)劃是(shi)整個后端流程(cheng)中(zhong)作重要的一(yi)步,但也(ye)是(shi)彈性最大的一(yi)步。因為(wei)沒有(you)標������準(zhun)的最佳方(fang)案,但又有(you)很多(duo)細(xi)節需(xu)要考量。? ? 布(bu)局�������(ju)布(bu)線的目標:優化芯(x�����in)片的面積,時序收斂,穩定,方便走(zou)線。? ? 工具:IC compiler,Encounter? ? 布圖(tu)規(gui)劃(hua)完成效(xiao)果(guo)圖(tu):

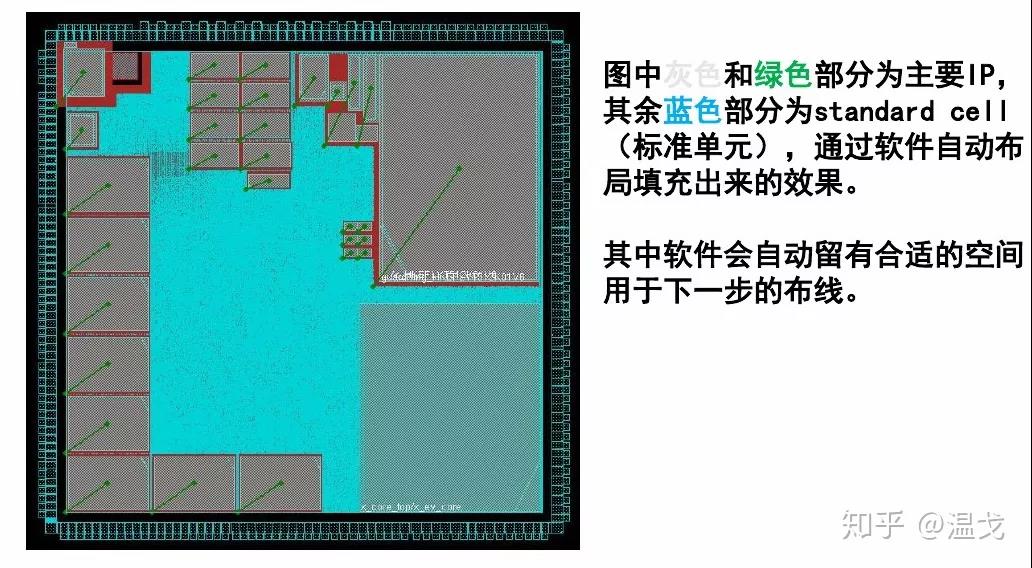

? ? 布局即(ji)擺放標準單元(yuan)(yuan),I/�����������O pad,宏單元(yuan)(yuan)來(lai)實現個電路邏輯(ji)。? ? 布(bu)局(ju)目(mu)標(biao):利用率越(yue��������)高越(yue)好,����總線長越(yue)短越(yue)好,時序越(yue)快越(yue)好。? ? 但(dan)利用�������率越(yue)(yue)高,布線(xian)就(jiu)越(yue)(yue)困難;總線(������xian)長(chang)越(yue)(yue)長(chang),時序就(jiu)越(yue)(yue)慢。因此要(yao)做到以上三個參數(shu)的最(zui)佳平(ping)衡。

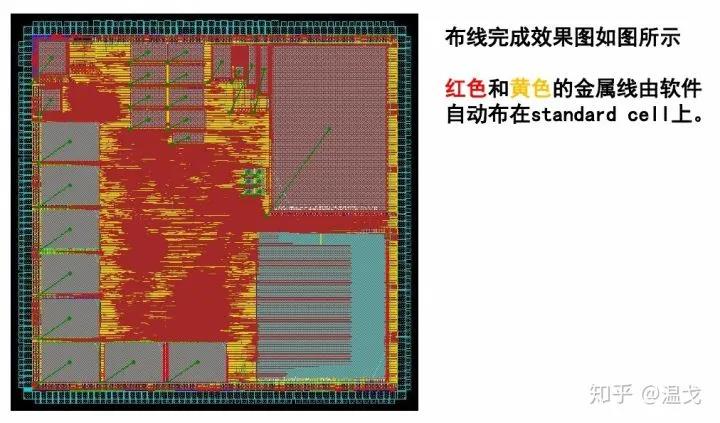

? ? 布(bu)線(xian)是指在(zai)滿(man)足工藝(yi)規(gui����)則和布(bu)線(xian)層數限(xian)制、線(xian)寬、線(xian)間距限(xian)制和各(ge)線(xian)網可靠(kao)絕緣的電(dian)性(xing)能約束條件下,根據電(dian)路的連(lian)接關系,將(jiang)各(ge)單元和I/O pad用互連(lian)線(xian)連(lian)接起來。

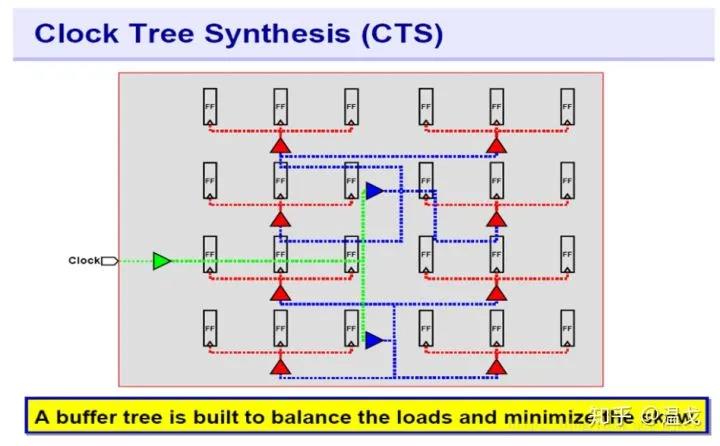

? ? 5.時(shi)鐘(zhong)樹綜合——CTS

? ? Clock Tree Synthesis,時鐘樹綜合,簡單點說就是時鐘的布線。

? ? 由于時(shi)(shi)鐘(zhong)(zhong)(zhong)(zhong)信(xin)號(hao)在數字芯片的(de)全局(ju)指揮作用,它的(de)分布應該是(shi)對稱式的(de)連到(dao)(dao)各個(ge)寄(ji)存(cun)器單(dan)元(yuan),從而使時(shi)(shi)鐘(zhong)(zhong)(zhong)(zhong)從同一個(ge)時(shi)(shi)鐘(zhong)(zhong)(zhong)(z�������hong)源到(dao)(dao)�����達(da)各個(ge)寄(ji)存(cun)器時(shi)(shi),時(shi)(shi)鐘(zhong)(zhong)(zhong)(zhong)延遲差異(yi)最小。這(zhe)也是(shi)為什么時(shi)(shi)鐘(zhong)(zhong)(zhong)(zhong)信(xin)號(hao)需要單(dan)獨(du)布線(xian)的(de)原因。

? ? 6. 寄(ji)生(sheng)參數提取(qu)

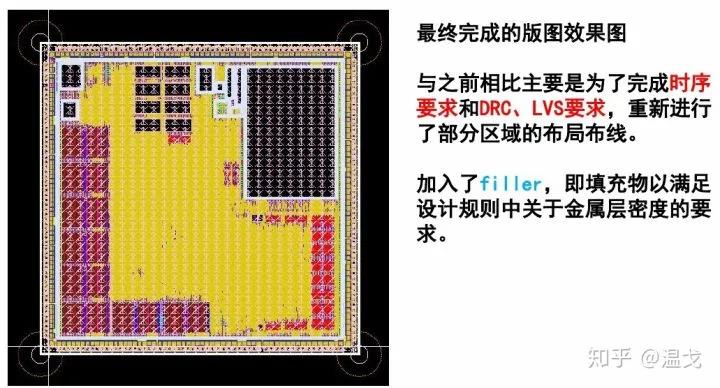

? ? 由于導線本身存在的電阻,相鄰導線之間的互感,耦合電容在芯片內部會產生信號噪聲,串擾和反射。這些效應會產生信號完整性問�������題,導致信號電壓波動和��������變化,如果嚴重就會導致信號失真錯誤。提取寄生參數進行再次的分析驗證,分析信號完整性問題是非常重要的。? ? 工(gong)具(ju)Synopsys的Star-RCXT? ? 這一環節是對完成布線(xian)的物理(li)版圖進(ji������������n)行功能和時序上的驗證(zheng),大概包含以下方面:? ? LVS(Layout Vs Schematic)驗證(zheng)(zheng):簡單說,就(jiu)是版圖(tu)與邏輯綜�������(zong)合(he)后(hou)的(de)門級電(dian)路圖(tu)的(de)對比(bi)驗證(zheng)(zheng);? ? DRC(Design Rule Checking)�����:設計規則檢查,檢查連(lian)線間距,連(lian)線寬度等是否(fou)滿足(zu)工藝要(yao)求;? ? ERC(Electrical Rule Checking):電(dia�������n)氣規(gui)則檢查(cha)(cha),檢查(cha)(cha)短(duan)路和開路等電(dian)氣規(gui)則違例;? ? 實際(ji)的后(hou)端(duan)流程還(huan)包括(kuo)電路功(gong)耗(hao)分析,以及隨著�����(zhu)制(zhi)造(zao)工(gong)藝不斷(duan)進(jin)步產生的DFM(可(ke)制(zhi)造(za�������o)性設(she)計)問(wen)題等。? ? 物理版圖以GDSII的文件格式交給芯片代工廠(稱為Foundry)在晶圓硅片上做出實際的電路。

GDSII效果版圖(tu)

? ? 最(zui)后(hou)進(jin)行封裝��������和測試,就得到了(le)我們實際看見的芯片(pi�������an)。

? ? 芯片設(she)計的(de)流(liu)程是紛繁復雜(za)的��������(de),從設(she)計到(dao)流(liu)片耗時長(chang)(�����一(yi)年(nian)甚至更久),流(liu)片成本高,一(yi)旦發(fa)現問(wen)題還(huan)要迭代(dai)之前的(de)某些過程