? ? 2021年,代工廠正在(zai)加(jia)緊各自5������nm甚至3nm先(xian)進工藝的(de)進程。與此同(tong)時,下游芯(xin)(xin)片(pian)商又必(bi)須在(zai)基(ji)于哪(na)種工藝設(she)計下一代芯(xin)(xin)片(pian)做出(chu)決定。這就可能影響到在(zai)3nm是延續現有的(de)FinFET發展,還是在(zai)3nm或2nm采用最新的(de)環(hua���n)柵晶體管(guan)技術(shu)(shu)。未來,隨(sui)著FinFET能力的(de)耗(hao)盡,芯(xin)(xin)片(pian)制造商還必(bi)須轉移到納(na)米片(pian)FET等更(geng)先(xian)進的(de)環(huan)柵技術(shu)(shu)…

? ? 從2007年高通首款采用65nm工藝的驍龍S1面世,到2021年即將問世的5nm工藝的驍龍875,處理器工藝節點實現了數代演進,性能、功耗、面積和成本都取得巨大發展。

? ? 有消息指出,在經過兩代7nm節點產品(驍龍855和865)由臺積電(TSMC)生產后,2021年,高通首款搭載5nm工藝的驍龍875將轉交三星生產。與此同時,蘋果的iPhone 12系列和iPad Air 2020中的A14 Bionic,以及華為Mate 40系列中所采用的麒麟9000芯片組,則都采用TSMC最新的5nm工藝生產。

? ? 一方(fang)面(mian),代工(gong)(gong)廠正在(zai)加緊各(ge)自5nm工(gong)(gong)藝(yi)的市場進(jin)程,另一方(fang)面(mian),下游芯片商又必須(xu)在(zai)基于5nm工(gong)(gong)藝(yi)設(she)計下一代芯片,還是(shi)轉向3nm或(huo)更先(xian)進(jin)�����節點之間做出決(jue)定。圖1:臺積電工藝節點路線圖。(圖片來源:WikiChip)? ? 這就可(ke)能影響到在(zai)3nm節(jie)(jie)點(dian)是(shi)(shi)延續現有的FinFET技術(shu)發展,還是(shi)(shi)在(zai)3nm或2nm節(jie)(jie)點(dian)采用最新的環柵(zha)晶(jing)體(ti)管(GAAFET)技術(shu)。GAAFET是(shi)(shi)從FinFET演變(bian)而(er)來(lai),這種新晶(jing)體(ti)管可(ke)提(ti)供更好的性(xing)能,但是(shi)(shi)難以制造(zao)、價格昂貴(gui),因此遷移起來(lai)就可(ke)能很痛苦。從好的方面來(lai)說������,業界正在(zai)開發新的蝕(shi)刻、圖(tu)案化等技術(shu),以幫助向這些節(jie)(jie)點(dian)發展鋪平道路。

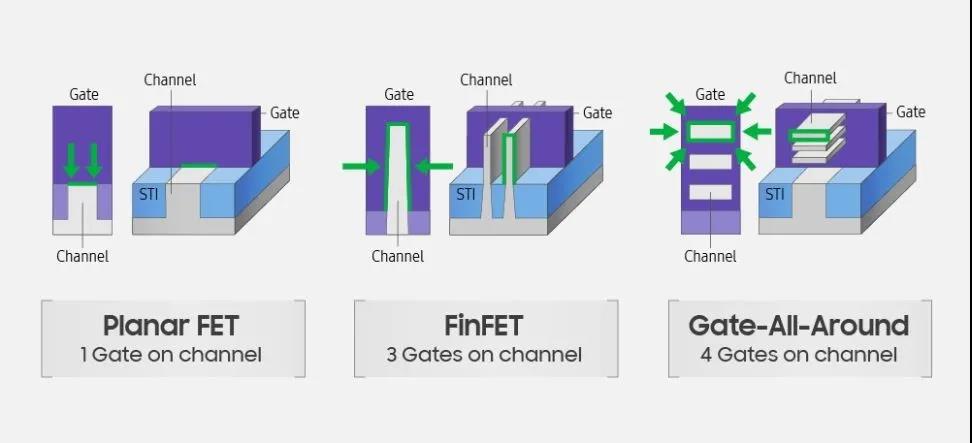

圖2:平面晶體管、FinFET與納米片FET三者對比。(圖片來源:三星)

微型(xing)化是(shi)否走到了盡頭?

? ? 芯片由三部分組成:晶體管、觸點和互連。晶體管用作器件中的開關。高級芯片擁有多達350億個晶體管。

? ? 互連位于晶體管的頂部,由微小的銅布線方案組成,用于將電信號從一個晶體管傳輸到另一個晶體管。晶體管和互連之間通過中間工序(MOL)連接,MOL由微小的接觸結構組成。

? ? IC微型化是推進設計的傳統方法,它是將每個工藝節點的晶體管規格縮小,然后將其集成到單個裸片上。

? ? 因此(ci),芯片制造商每18到24個(ge)月就會通過晶(jing)(jing)體(ti)管(guan)密(mi)度(du)的提高(gao)而推出一(yi)種�����新工藝技術������。每種工藝都會取一(yi)個(ge)數字節(jie)點(dian)名稱(cheng)。最初,節(jie)點(dian)名稱(cheng)與晶(jing)(jing)體(ti)管(guan)柵極長度(du)尺寸(cun)相(xiang)關。

? ? 在每個節點上,芯片的晶體管規格都是微縮0.7倍,這樣,在相同的功率下性能就提高40%,面積就減少50%。芯片微型化技術讓新的電子產品實現了更多功能。

芯片制造商在邁向各個工藝節點的過程中都遵循這個趨勢。但是,到20nm時,傳統的平面晶體管就行不通了,這時就發生了很大的改變。從2011年開始,芯片制造商開始向FinFET遷移,從而延續摩爾定律的發展。

? ? 然而,FinFET制造起來更燒錢。結果,工藝研發成本猛增。因此,現在完全微縮節點的節奏從18個月延長到了30個月,甚至更長。

? 在(zai)高(gao)級(ji)節點上(shang)(shang),英(ying)特爾(er)繼續遵循0.7倍的�����微縮趨(qu)勢。但(dan)是從16nm/14nm開始,其他廠商偏(pian)離了(le)這個趨(qu)勢,這就在(zai)市(shi)場上(shang)(shang)造成了(le)一定混亂。

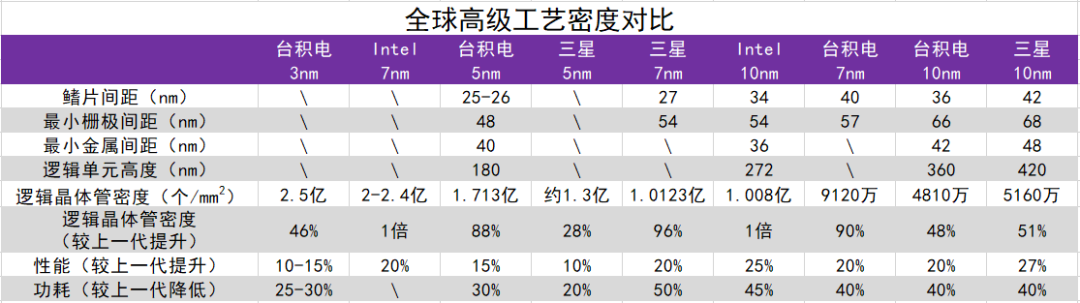

圖3:全球高級工藝密度對比。

? ? 那時,節點名稱變得模糊,不再與任何晶體管規格相關。今天,節點名稱只不過是市場術語,這個指標變得越來越沒有意義和具有誤導性。例如,在5nm或3nm節點,幾何圖形不再是5nm或3nm。此外,供應商之間的工藝通用性大大降低。對于同一節點,從臺積電到三星,還有英特爾,性能不再相同。

? ? 高級節點的微型化速度也在放緩。通常,7nm工藝的接觸式多晶間距(CPP),其范圍從56nm至57nm,金屬間距為40nm。到5nm,CPP約為45nm-50nm,金屬間距為26nm。CPP是一個關鍵的晶體管指標,用于度量源極和漏極觸點之間的距離。

? ? 另外,價格/性能優勢不再遵循相同的曲線,因此許多人都認為摩爾定律已走到了盡頭。

? ? 隨(sui)著多重圖案和EUV成(cheng)(cheng)本(ben)的增加,摩爾定律的經濟方面開(kai)始下降(jiang)。未來(lai),計算能力的提(ti)高可能來(lai)自新的設計和體系(xi)結構而不是(shi)微型(xing)化。也即未來(l�������ai)芯�������片的計算能力將會繼續提(ti)高,但其成(cheng)(cheng)本(ben)的下降(jiang)速度不一定再(zai)與過去相同。

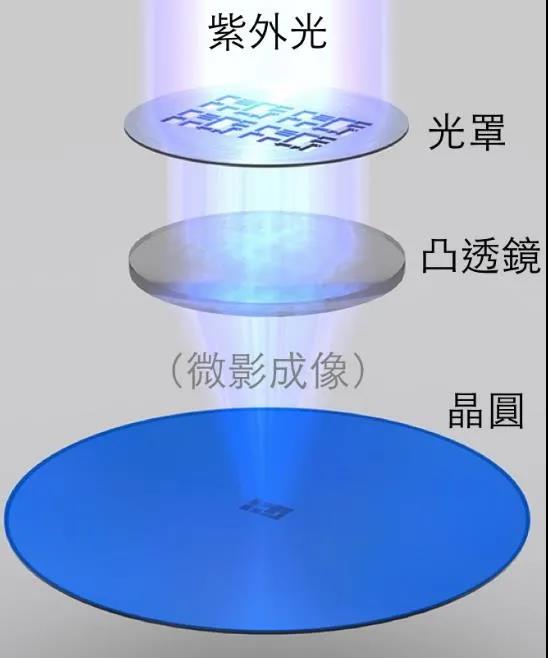

圖4:光刻原理。

? ? 芯片微型化并沒有完全消失。人工智能、服務器和智能手機等對更快芯片的追求推動了高級節點的發展。但是,并不是所有人都需要高級節點。成熟工藝芯片的需求仍然旺盛,例如5G智能手機中所使用的RF IC和OLED驅動器IC,以及面向計算和固態驅動器應用設計的電源管理IC。

? ? FinFET微型化

? ? 同時,在芯片微型化方面,多年來芯片制造商都遵循相同的工藝路線圖,并且晶體管類型相同。2011年,英特爾在22nm轉向FinFET,其他代工廠則是從16nm/14nm開始。

? ?在FinFET中,電流的控制是通過在鰭片的三個側面分別制造柵極而實現的。每個FinFET具有兩到四個鰭。每個鰭片都有不同的寬度、高度和形狀。

? ? 英特爾第一代22nm FinFET的鰭片間距為60nm,鰭片高度為34nm。然后,在14nm,英特爾FinFET的鰭片間距和高度都變成42nm。

? ? 因此,英特爾是通過將鰭片做高做薄來實現FinFET的微型化。

? ? 在10nm/7nm上,芯片制造商遵循相同的方法來實現FinFET微型化。臺積電在2018年推出了首個7nm FinFET工藝,隨后是三星。同時,英特爾在經歷了幾次延誤后于2019年實現10nm出貨。

? ? 未來,代工行業的競爭將更加激烈。三星和臺積電正在加大5nm和各種半節點產品的生產和3nm的研發。

? ? 與7nm相比,三星的5nm FinFET技術可將邏輯面積最多增加25%,功耗降低20%,性能提高10%。

? ? 相比之下,TSMC的5nm FinFET工藝在相同的功耗下速度提高15%,或者在相同速度下功耗降低30%,邏輯密度為7nm節點的1.84倍。

? ? 芯片制造商在7nm和5nm節點進行了一些重大改變。為了對芯片中的關鍵特征實現圖案化,兩家公司從傳統的193nm光刻技術過渡到了極紫外(EUV)光刻技術。使用13.5nm波長的EUV可以對此進行簡化。

? ? 但EUV不能解決芯片微縮方面的所有挑戰。解決這些挑戰需要使用多種技術,除了微型化外,還包括新材料的使用、新型嵌入式非易失性存儲器和高級邏輯架構、沉積和蝕刻新方法,以及封裝和小芯片設計的創新。

? ? 同時,三星和臺積電也在默默準備3nm工藝。過去,芯片制造商遵循相同的路線,但是今天卻出現了分歧。

? ? 3nm可能有幾種不同的方案,例如FinFET和環柵。這樣客戶就可以根據自己的需求在成本、密度、功耗和性能方面做出權衡。

? ? 如前所述,三星將推出3nm的納米片FET。臺積電也在對此進行研究,但其計劃將FinFET延續到下一代。該公司將在2021年第三季度推出3nm FinFET,環柵則是在2022或2023年左右。對此,下游芯片商必須在成本和技術之間做出折衷。延續FinFET是一條更安全的途徑,因此許多芯片商認為臺積電是一家低風險供應商。

? ? 不過,在某種程度上,環柵技術可提供更高的性能。據悉,與3nm FinFET相比,3nm環柵具有較低的閾值電壓,并且有可能將功耗降低15%至20%。但是,由于MOL和后道工序(BEOL)相同,因此性能差異可能會低于8%。BEOL和MOL是高級芯片的瓶頸,接觸電阻是MOL中的一個問題。

? ? BEOL用于實現芯片內的銅互連。在每個節點,由于互連尺寸變得越來越小,芯片中的阻容(RC)延遲問題變得嚴重。雖然FinFET和環柵晶體管類型不同,但它們在3nm可能具有類似的銅互連方案。RC延遲對于兩種晶體管都是一個問題。

? ? 還有其他挑戰。當鰭片寬度達到5nm時,FinFET就行不通了。5nm/3nm FinFET遇到了這個極限。

? ? 另外,與其他節點有兩個或更多鰭片相比,3nm FinFET可能只有一個鰭片。這就對鰭片的驅動功率提出更高的要求。

? ? 將FinFET擴展到3nm的一種方法是使用鍺材料作為p溝道。具有高遷移率溝道的3nm FinFET可提高性能,但存在一些集成挑戰。

? ? 轉向(xiang)納米片FET

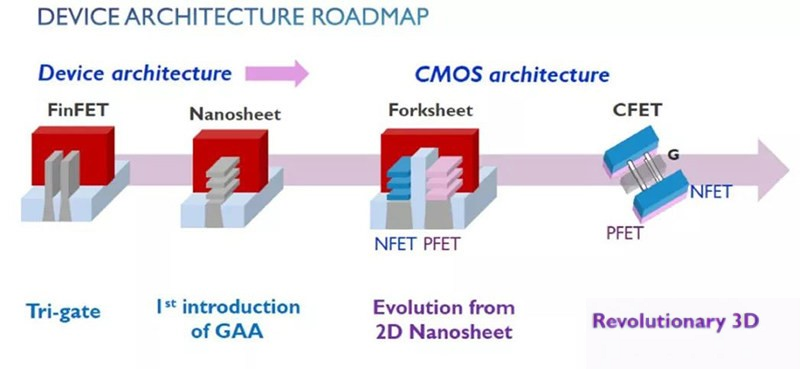

? ? 最終,FinFET微型化將會停止,因此芯片制造商必須轉移到新的晶體管,即納米片FET或相關類型。

? ? 納米片FET的勢頭始于2017年,當時三星推出了3nm的多橋溝道FET(MBCFET)——MBCFET是一種納米片FET(納米片FET又是一種環柵晶體管)。其量產定于2022年開始。

? ? 臺積電也在研究納米片。與5nm FinFET相比,納米片提供了適當的微縮,而且具有一些優勢。

? 納米片FET的側面基本上是個FinFET,然后柵極包裹在其周圍。納米片由幾個分開的、垂直堆疊的水平薄片組成。每個薄片形成一個溝道。

? ? 柵極圍繞在每個薄片周圍,從而形成環柵晶體管。從理論上講,由于電流的控制是在這種結構的四個側面完成的,因此納米片FET可以提供更高的性能,并且漏電更少。

? ? 最初,納米片會有四個左右的薄片。典型的納米片寬度為12nm至16nm,厚度為5nm。這就是納米片不同于FinFET的地方。FinFET用有限數量的鰭片進行量化,這對設計人員提出了一些限制。納米片的優勢在于它可以具有不同的納米片寬度。根據設計人員的需求,每個器件可以具有不同的寬度。這為設計人員提供了一些自由,并能在性能和功耗方面實現更好的平衡。

? ? 例如,具有較寬薄片的晶體管可以實現更大的驅動電流。具有較窄的薄片可以實現較小的器件,但是驅動電流較小。

? ??納米片與納米線有關。納米線是用電線而非薄片形成溝道,溝道寬度有限,因此驅動電流較小。

? ??這就是納米片FET蒸蒸日上的原因。但是,在3nm左右,這項技術和FinFET面臨一些挑戰。FinFET面臨的挑戰是在微縮柵極長度的情況下對鰭片寬度和鰭片輪廓進行量子控制。納米片面臨的挑戰是n/p失衡、底片效率、間隔層、柵極長度控制和器件覆蓋率。

? ??考慮到這些挑戰,納米片FET將需要時間來加速。

? ??在簡單的工藝流程中,納米片FET開始于在襯底上形成超晶格結構。外延工具在襯底上交替沉積多層硅鍺(SiGe)和硅材料——至少包含三層SiGe和三層硅。然后使用圖案化和蝕刻在超晶格結構中形成垂直鰭,超晶格結構和鰭片形成需要精確的CD控制。

? ??隨后的工序就比較麻煩了:內間隔層的形成。首先要使超晶格結構中的SiGe層的外部凹陷。這樣就能產生小空間而充滿電介質材料。內間隔層用于減少柵極到源極/漏極的電容,其制程控制非常關鍵。

? ??作為解決方案,IBM和東電電子(TEL)最近面向內間隔層和溝道釋放過程發表了一種新蝕刻技術。涉及比率為150:1的各向同性SiGe干法蝕刻技術。這項技術可實現精確的內間隔層。

? ??然后就可以形成源極/漏極。再然后,使用蝕刻工藝去除超晶格結構中的SiGe層,所剩下的是構成溝道的硅基層或者片。

? ??高k/金屬柵材料沉積在這一結構中。最后,形成MOL和銅互連,從而形成納米片。

? ??上述即為這個復雜過程的簡單描述。但是,與任何新技術一樣,納米片也容易出現缺陷,這需要在晶圓廠進行更多的檢查和度量。

更多(duo)方案

? ??Imec正在研發更先進的環柵形式,例如CFET和����������forksheet FET,它們的目標是2nm及以后。

圖5:晶體管結構進化路線圖。

? ??屆時,對于大多數人來說,IC微型化可能就太燒錢了,特別是存在功�����耗和性能優勢的降低。這就是高級封裝技術變得越來越有吸引力的原因。不是將所有芯片功能都塞在同一個裸片上,而是將器件分解成更小的裸片,然后將它們集成到高級封裝中。

? ??當然,這取決于應用。即使在深亞微米節點,也會出現更多這類活動。有許多公司正在研究它,在決定有哪些內容不能或不希望在5nm上集成,也即研究如何對系統進行分割。

? ??這不是那么容易。此外,還有幾種封裝方案可以選擇,例如2.5D、3D IC,小芯片和扇出,它們各有各������的折衷。

總結

? ??可以肯定地說,并不是所有人都需要高級節點。但是無疑,蘋果、海思、英特爾、三星和高通都需要各種先進技術。

? ??消費者希望擁有性能更高、最新最好的系統。最大的問題是,下一代技術是�����否能以合適的成本提供任何真正的優勢。