? ? 隨(sui)著科(ke)學技術(shu)的(de)發(fa)展,日益廣泛采用(yong)的(de)微電子技術(shu)和(he)電氣化的(de)逐步(bu)實現,形成了(le)復雜的(de)電磁環境。有(you)些(xie)產品在雷(lei)雨季節時運行,經常(chang)會有(you)大量部件損壞;還有(you)一(yi)些(xie)產品��,在實驗調試階段,每(me�����i)一(yi)樣(yang)指(zhi)標、性能都完美適配(pei),但到了(le)客戶手里卻小毛病(bing)不斷。

? ? 這些問題當(dang)中,有(you)相(xiang)當(dang)一部分(fen)都源(yuan)于電(dian)磁干(gan)擾。所以(yi),不斷(duan)研究和解(�����jie)決電(dian)磁環境中設備(bei)之(zhi)間以(yi)及系(xi)統(tong)間相(xiang)互關(guan)系(xi)的問題,促進了電(dian)磁兼容(rong)技(ji)術的迅速發展(zhan)。

電磁干擾

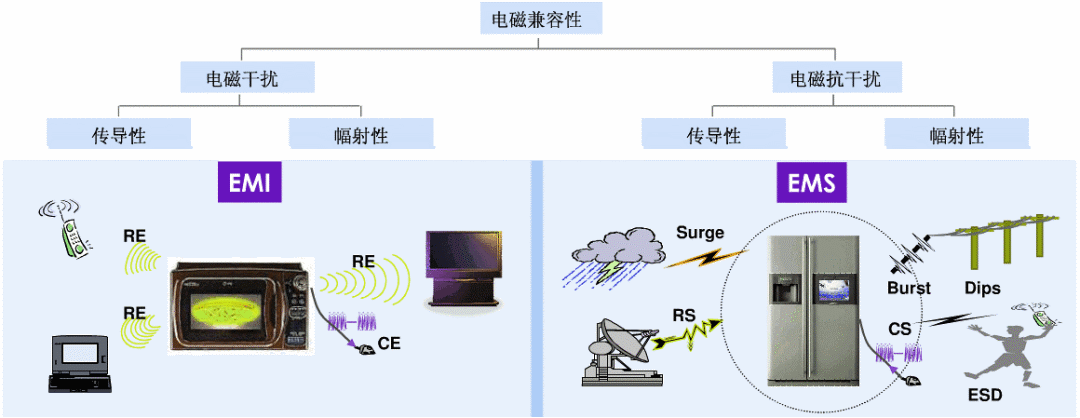

? ? 電(dian)(dian)磁(ci)(ci)兼��������容(EMC)是設備或系統在其電(dian)(dian)磁(ci)(ci)環境(jing)中能正常工(gong)作且不(bu)對該環境(jing)中任何事物構成不(bu)能承受的電(dian)(dian)磁(ci)(ci)干(gan)擾的能力(li)。

? ? EMC由(you)兩部分(fen)構成:電(dian)(dian)磁(ci)干(gan)擾(rao)(EMI)和電(dian)(dian)磁(ci)抗擾(rao)度(EMS),電(dian)(dian)磁(ci)干(gan)擾(rao)是指設備或(huo)系(xi)統對外(wai)發射的干(gan)擾(rao),不能(neng)(neng)超過限值;而電(dian)(dian�������)磁(ci)抗擾(rao)度是指設備或(huo)系(xi)統能(neng)(neng)夠抵抗外(wai)界環境(jing)電(dian)(dian)磁(ci)干(gan)擾(rao)的最(zui)小值。

? ? 電磁干擾形成的(de)三要素分別為干擾源(yuan),傳播(bo)(bo)途徑以及(ji)敏感(gan)設(she)備(bei)。一般情況下(xia)EMI整改往往是從干擾源(yuan)以及(ji)傳播(bo)(bo)路(lu)徑上入(������ru)手的(de),即抑制干擾源(yuan)和切斷傳播(bo)(bo)路(lu)徑。

EMI抑制方案

? ? 以音頻產品為例(li),抑制(zhi)傳導EM������I措施主要可分為抑制��������(zhi)干擾(rao)源以及(ji)傳播(bo)路(lu)徑的優化兩大方向。

01.抑制干擾源方向

D類功放產(chan)品存(cun)在������功率管高頻開關(guan)動作,這樣(yang)勢(shi)必會造成較(jiao)差的������傳導EMI進(jin)而影(ying)響系統中其他電路,矽力杰現有產(chan)品中有如下優化措施:

1. 抖頻技術:

將原來單一(yi)(yi)的��������(de)開(kai)關頻率擴展到(dao)一(yi)(yi)定的(de)范圍內,從而降低頻譜中(zhong)單個尖峰的(d������e)高度。

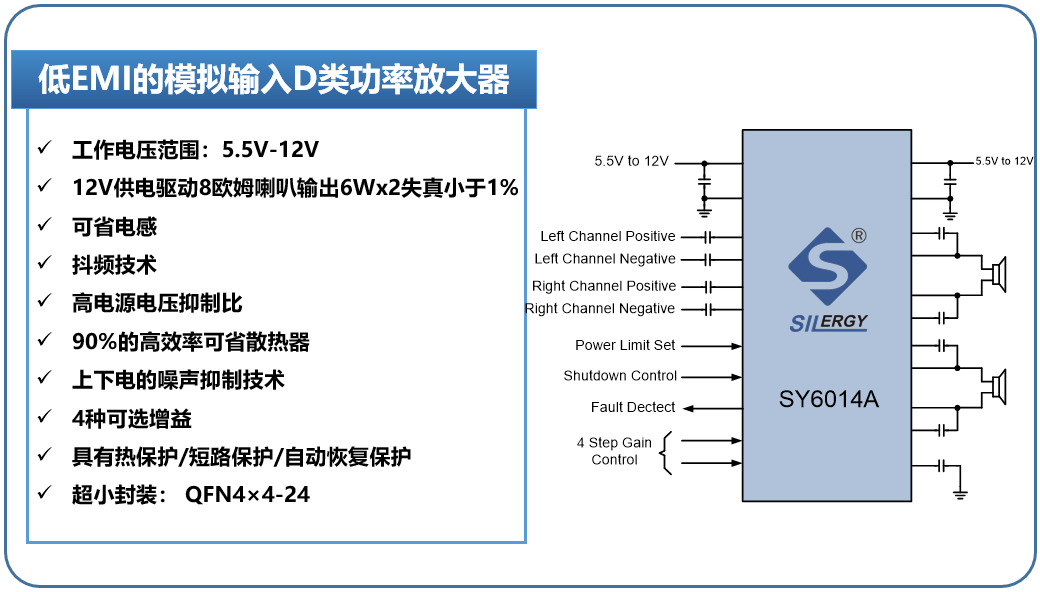

SY6014/SY6014A是高性能(neng)模(mo)擬D類功放芯片,采用偽隨機頻率抖動技術,將原本的單(dan)一峰(�������feng)值能(neng)量(liang)擴(kuo)展為一個(ge)頻帶(dai)的平均能(neng)量(liang),使得(de)該頻帶(dai)內的峰(feng)值能(neng)量(liang)下降(jiang)6dB。

2. 相位延遲技術:

針對(dui)多通道輸出的產���������品(pin),�������將(jiang)各路的PWM輸出之間增加相位延遲,進而減小(xiao)頻譜上對(dui)應頻率的峰(feng)值。

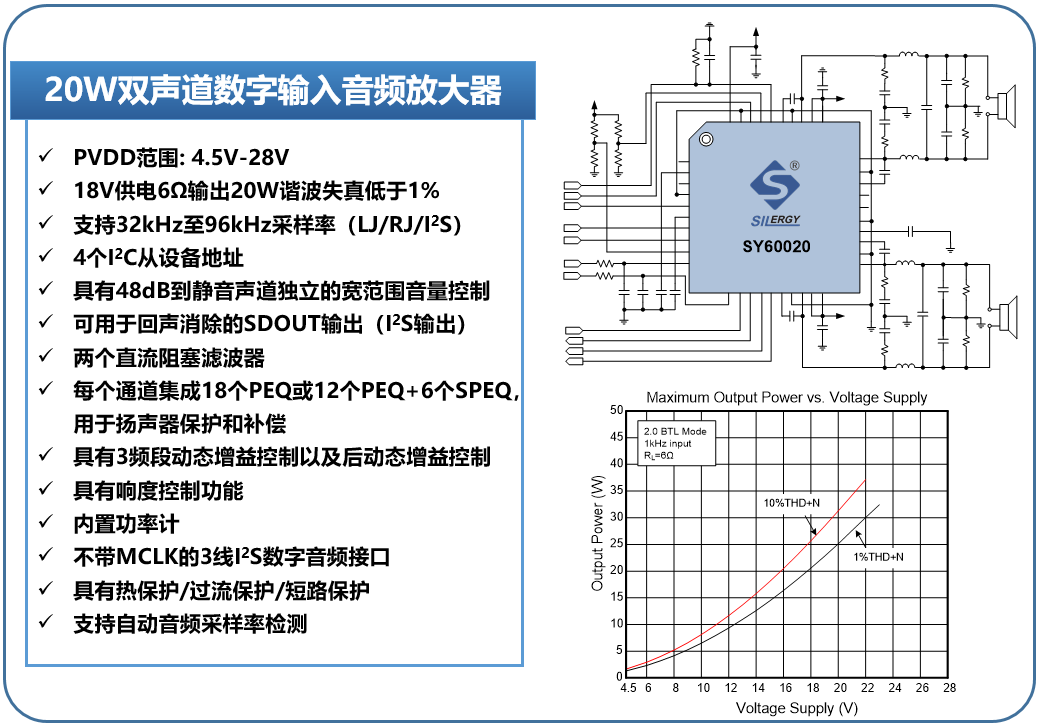

SY6045B/SY60020是I2S輸入集(ji)成(cheng)高性(xing)能(neng)DSP支持雙(shuang)通(tong)道的數字輸入音頻放大器, 其(qi)每一路的驅動部分均可以通(tong)過(guo)I2C設置������相位(wei)延遲, 在電視應用中(zhong),通(tong)過(guo)調節相位(wei)延遲, 使其(qi)在不影響音頻性(xing)能(ne���������ng)的前(qian)提下,EMI傳導干擾降(jiang)低(di)5.5dB。

3. 邊沿控制技術:

優(you)化驅動(dong)電(dian)路,有效控制開關上(shang)升下降沿(yan),減(jian)少輸出(chu)邊沿(yan)的(de)振鈴。������矽(xi)力杰模(mo)擬/數字(zi)音頻������功放芯片中皆進(jin)行了功率管(guan)驅動(dong)電(dian)路的(de)優(you)化。

4. 增加緩沖電路:

在PWM輸出節點增加合(he)適的(de)緩(huan)沖電路,���可(ke)以改(gai)善邊(bian)沿時間,從而改(gai)善�������EMI。

02.傳播路徑的優化

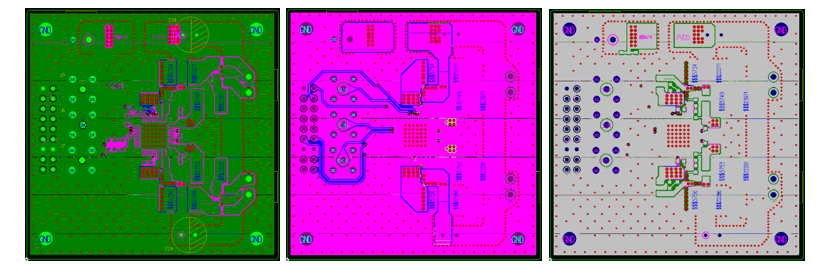

傳播路徑(jing)的優(you)化(hua)主要可通過優(you)化(hua)PCB布(bu)局布(bu)線來提������高抗電磁干(gan)擾性(xing)能。

1. 地平面屏蔽:

盡量將功(gong)率(lv)走線和信號(hao)走線��������置于中(zhong)間層(ceng),用頂層(ceng)和底層(ceng)整片(pian)的地(di)平面(mian)包圍(wei)。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 頂層:接地? ? ? ? ? ? ? ? ? ?������� ? ? ? ? ? ? ? ? ? ? ?中間層:信號/�������電源? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?底層:接地

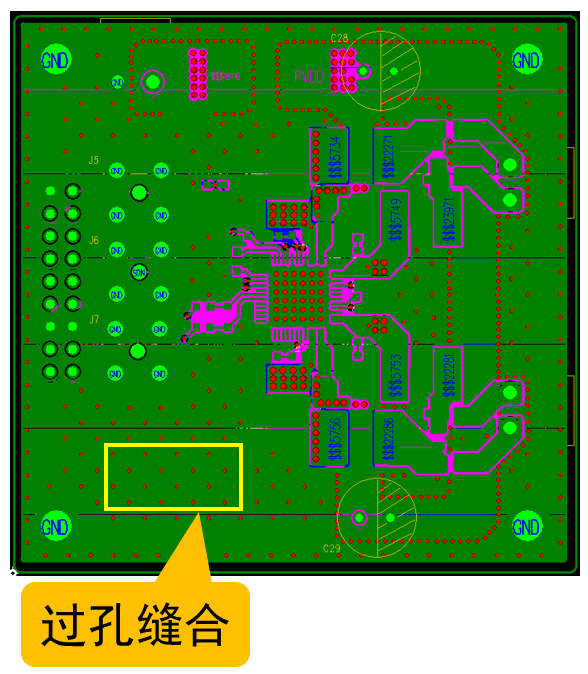

2. 過孔縫合:

將所有的(de)地平面使用(yong)大(da)量�������等(deng)間距的(de)過孔������連接(jie)起來。

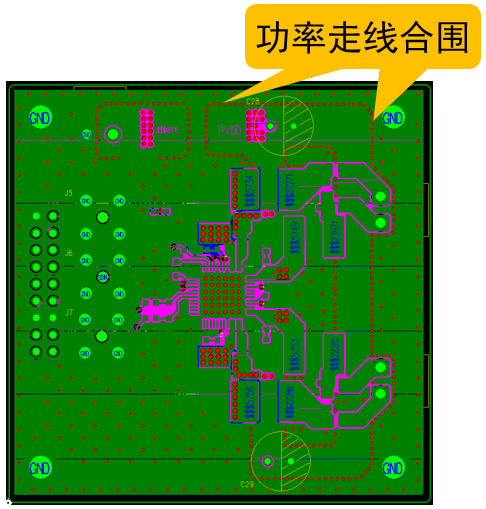

3.?功率走線(xian)合圍:

同������(tong)樣用(yong)過孔沿功率走線均勻布������置以提供(gong)最近(jin)的低阻抗路徑(jing)

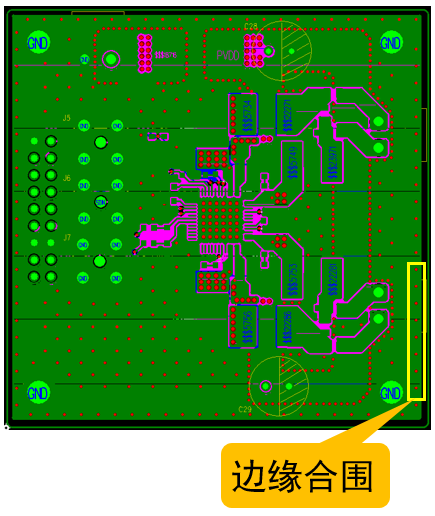

4. 邊緣合圍:

將PCB板邊緣同樣(yang)用過(guo)孔合圍(wei�������),可以減小板邊緣的電容效應(ying)從而改(gai)善EMI。

? ? 在(zai)音頻(pin)領(ling)域(yu)中,電磁干擾(rao)不(bu)僅(jin)會(hui)影響產品(pin)的(de)工作可靠性,還(huan)經常會(hui)耦合到音頻(pin)信號的(de)路徑中。低(di)EMI電路設計可以避免不(bu)必要的(de)PCB重(zhong)新(xin)制造,節省開發成本和時間,確(que)保(bao)電子產品(pin)按(an)時甚(shen)至提前進(jin)入消�������������費者視野。